# STK531U369A-E

www.onsemi.com

# **Inverter IPM** for 3-phase Motor Drive

#### Overview

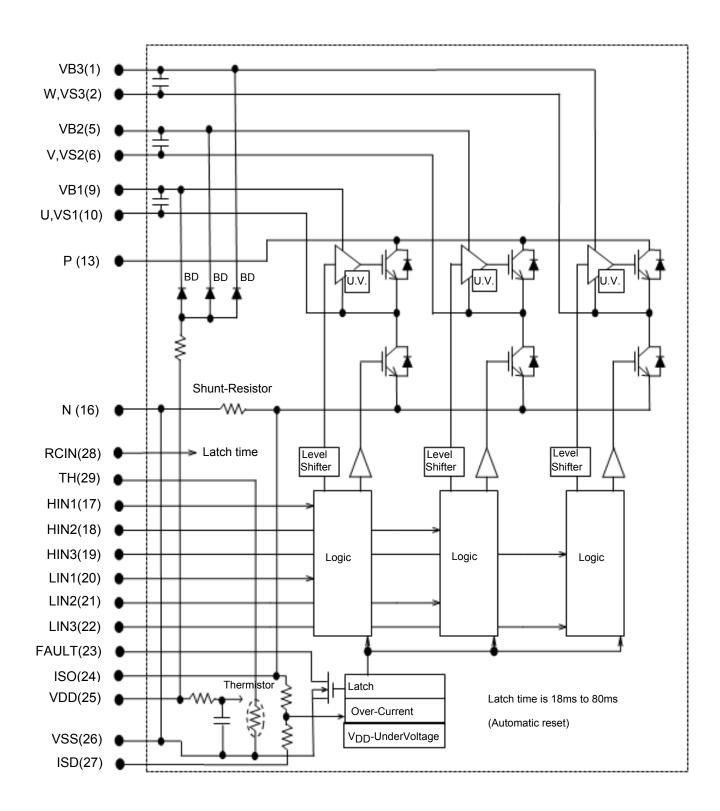

This "Inverter IPM" is highly integrated device containing all High Voltage (HV) control from HV-DC to 3-phase outputs in a single SIP module (Single-In line Package). Output stage uses IGBT/FRD technology and implements Under Voltage Protection (UVP) and Over Current Protection (OCP) with a Fault Detection output flag. Internal Boost diodes are provided for high side gate boost drive.

#### **Function**

- Single control power supply due to Internal bootstrap circuit for high side pre-driver circuit

- All control input and status output are at low voltage levels directly compatible with microcontrollers

- Built-in cross conduction prevention

- Externally accessible embedded thermistor for substrate temperature measurement

- The level of the over current protection is adjustable with the external resistor, "RSD"

#### Certification

• UL Recognized (File number : E339285)

#### **Specifications**

Absolute Maximum Ratings at Tc = 25°C

| Parameter                  | Symbol          | Remarks                                                          | Ratings                 | Unit |

|----------------------------|-----------------|------------------------------------------------------------------|-------------------------|------|

| Supply voltage             | V <sub>CC</sub> | P to N, surge < 500V *                                           | 1 450                   | V    |

| Collector-emitter voltage  | V <sub>CE</sub> | P to U, V, W or U, V, W, to N                                    | 600                     | V    |

| Output ourrent             | la la           | P, N, U, V, W terminal current                                   | ±10                     | А    |

| Output current             | lo              | P, N, U, V, W terminal current at Tc = 100°C                     | ±5                      | А    |

| Output peak current        | lop             | P, N, U, V, W terminal current, PW = 1ms                         | ±20                     | А    |

| Pre-driver voltage         | VD1,2,3,4       | VB1 to U, VB2 to V, VB3 to W, V <sub>DD</sub> to V <sub>SS</sub> | 2 20                    | V    |

| Input signal voltage       | VIN             | HIN1, 2, 3, LIN1, 2, 3                                           | −0.3 to V <sub>DD</sub> | V    |

| FAULT terminal voltage     | VFAULT          | FAULT terminal                                                   | −0.3 to V <sub>DD</sub> | V    |

| Maximum power dissipation  | Pd              | IGBT per 1 channel                                               | 31.2                    | W    |

| Junction temperature       | Tj              | IGBT, FRD                                                        | 150                     | °C   |

| Storage temperature        | Tstg            |                                                                  | -40 to +125             | °C   |

| Operating case temperature | Tc              | IPM case temperature                                             | -20 to +100             | °C   |

| Tightening torque          |                 | A screw part *:                                                  | 0.9                     | Nm   |

| Isolation voltage          | Vis             | 50Hz sine wave AC 1 minute *                                     | 2000                    | VRMS |

Reference voltage is "VSS" terminal voltage unless otherwise specified.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed damage may occur and reliability may be affected.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 13 of this data sheet.

<sup>\*1 :</sup> Surge voltage developed by the switching operation due to the wiring inductance between P and N terminal.

<sup>\*2</sup>: VD1=VB1 to U, VD2=VB2 to V, VD3=VB3 to W, VD4=V<sub>DD</sub> to V<sub>SS</sub> terminal voltage.

<sup>\*3:</sup> Flatness of the heat-sink should be lower than 0.15mm.

<sup>\*4:</sup> Test conditions: AC2500V, 1 second.

#### Electrical Characteristics at Tc = 25°C, VD1, VD2, VD3, VD4 = 15V

| Parameter                                                    | Symbol                                    | Conditions             |                | Test<br>circuit | MIN  | TYP  | MAX  | Unit  |  |

|--------------------------------------------------------------|-------------------------------------------|------------------------|----------------|-----------------|------|------|------|-------|--|

| Power output section                                         |                                           |                        |                |                 |      |      |      |       |  |

| Collector-emitter cut-off current                            | ICE                                       | V <sub>CE</sub> = 600V |                | Fig. 4          | -    | -    | 0.1  | mA    |  |

| Bootstrap diode reverse current                              | IR(BD)                                    | VR(BD) = 600V          |                | Fig.1           | -    | -    | 0.1  | mA    |  |

|                                                              |                                           | Ic = 10A               | Upper side     |                 | -    | 1.9  | 2.4  |       |  |

| Callegtor to amitter acturation valtage                      | V <sub>CF</sub> (SAT)                     | Tj = 25°C              | Lower side *1  | Fig 0           | -    | 2.2  | 2.7  | V     |  |

| Collector to emitter saturation voltage                      | VCE(O/11)                                 | Ic = 5A                | Upper side     | Fig.2           | -    | 1.5  | -    | V     |  |

|                                                              |                                           | Tj = 100°C             | Lower side *1  |                 | -    | 1.7  | -    |       |  |

|                                                              |                                           | IF = 10A               | Upper side     |                 | -    | 1.8  | 2.1  |       |  |

| D                                                            | VF                                        | Tj = 25°C              | Lower side *1  | F: 0            | -    | 2.1  | 2.4  | V     |  |

| Diode forward voltage                                        | VF                                        | IF = 5A                | Upper side     | Fig.3           | -    | 1.4  | -    | V     |  |

|                                                              | Tj = $100^{\circ}$ C Lower side *1        |                        | -              | 1.6             | -    |      |      |       |  |

| Junction to case                                             | θj-c(T)                                   | IGBT                   |                |                 | -    | -    | 4.0  | 00001 |  |

| thermal resistance                                           | θj-c(D)                                   | FWD                    |                | ] -             | -    | -    | 6.0  | °C/W  |  |

| Control (Pre-driver) section                                 |                                           |                        |                |                 |      |      |      |       |  |

| Dec deitre comment commention                                | ID                                        | VD1, 2, 3 = 15V        |                | Fig. 4          | -    | 0.08 | 0.4  | ^     |  |

| Pre-driver current consumption                               | ID                                        | VD4 = 15V              |                | Fig.4           | -    | 1.6  | 4.0  | mA    |  |

| High level Input voltage                                     | Vin H                                     | HIN1, HIN2, H          |                |                 | 2.5  | -    | -    | V     |  |

| Low level Input voltage                                      | Vin L                                     | LIN1, LIN2, LII        | N3 to $V_{SS}$ |                 | -    | -    | 0.8  | V     |  |

| Input threshold voltage hysteresis *2                        | Vinth(hys)                                |                        |                |                 | 0.5  | 0.8  | -    | V     |  |

| Logic 1 input leakage current                                | I <sub>IN+</sub>                          | VIN = +3.3V            |                |                 | -    | 100  | 143  | μΑ    |  |

| Logic 0 input leakage current                                | I <sub>IN</sub> _                         | VIN = 0V               |                |                 | -    | -    | 2    | μA    |  |

| FAULT terminal sink current                                  | IoSD                                      | FAULT : ON / \         | VFAULT = 0.1V  |                 | -    | 2    | -    | mA    |  |

| FAULT clear time                                             | FLTCLR                                    | Fault output la        | tch time       |                 | 18   | -    | 80   | ms    |  |

| V <sub>CC</sub> and VS undervoltage positive going threshold | V <sub>CCUV+</sub><br>V <sub>SUV+</sub>   |                        |                |                 | 10.5 | 11.1 | 11.7 | V     |  |

| V <sub>CC</sub> and VS undervoltage negative going threshold | V <sub>CCUV</sub> _<br>V <sub>SUV</sub> _ |                        |                |                 | 10.3 | 10.9 | 11.5 | V     |  |

| V <sub>CC</sub> and VS undervoltage hysteresis               | V <sub>CCUVH</sub><br>V <sub>SUVH</sub>   |                        |                |                 | 0.14 | 0.2  | -    | V     |  |

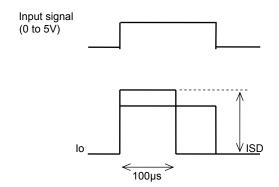

| Over current protection level                                | ISD                                       | PW = 100µs, F          | RSD = 0Ω       | Fig.5           | 18.1 | -    | 22.9 | Α     |  |

| Electric current output signal level                         | ISO                                       | Io = 10A               |                | -               | 0.31 | 0.33 | 0.35 | V     |  |

Reference voltage is "VSS" terminal voltage unless otherwise specified.

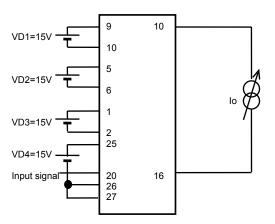

#### Electrical Characteristics at Tc = 25°C, VD1, VD2, VD3, VD4 = 15V, V<sub>CC</sub> = 300V, L = 3.9mH

| Parameter                         | Symbol | Conditions                         | Test<br>circuit | MIN         | TYP | MAX | Unit |

|-----------------------------------|--------|------------------------------------|-----------------|-------------|-----|-----|------|

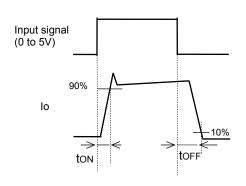

| Switching time                    | tON    | lo = 10A                           |                 | 0.3         | 0.5 | 1.2 |      |

| Switching time                    | tOFF   | - 10 = 10A                         |                 | -           | 0.8 | 1.5 | μs   |

| Turn-on switching loss            | Eon    |                                    |                 | -           | 200 | -   | μJ   |

| Turn-off switching loss           | Eoff   | Io = 5A                            | Fin 6           | -           | 130 | -   | μJ   |

| Total switching loss              | Etot   | ]                                  | Fig.6           | -           | 330 | -   | μJ   |

| Turn-on switching loss            | Eon    |                                    |                 | -           | 240 | -   | μJ   |

| Turn-off switching loss           | Eoff   | Io = 5A, Tc = 100°C                |                 | -           | 130 | -   | μJ   |

| Total switching loss              | Etot   | ]                                  |                 | -           | 370 | -   | μJ   |

| Diode reverse recovery energy     | Erec   | IF - 54 D - 400V To - 100°C        |                 | -           | 17  | -   | μJ   |

| Diode reverse recovery time       | trr    | IF = 5A, P = 400V, Tc = 100°C      |                 | -           | 62  | -   | ns   |

| Reverse bias safe operating area  | RBSOA  | Io = 20A, V <sub>CE</sub> = 450V   |                 | Full square |     |     |      |

| Short circuit safe operating area | SCSOA  | V <sub>CE</sub> = 400V, Tc = 100°C |                 | 4           | -   | -   | μs   |

Reference voltage is " $V_{SS}$ " terminal voltage unless otherwise specified.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### Notes:

- $1. \ The \ pre-drive \ power \ supply \ low \ voltage \ protection \ has \ approximately \ 0.2V \ of \ hysteres is \ and \ operates \ as \ follows.$

- Upper side: The gate is turned off and will return to regular operation when recovering to the normal voltage, but the latch will continue till the input signal will turn 'high'.

- Lower side: The gate is turned off and will automatically reset when recovering to normal voltage. It does not depend on input signal voltage.

- 2. The pre-drive low voltage protection is the feature to protect devices when the pre-driver supply voltage falls due to an operating malfunction.

<sup>\*1</sup>: The lower side's  $V_{CE}(SAT)$  and VF include a loss by the shunt resistance

<sup>\*2:</sup> Input threshold voltage hysteresis indicates a reference value based on the design value of built-in pre-driver IC

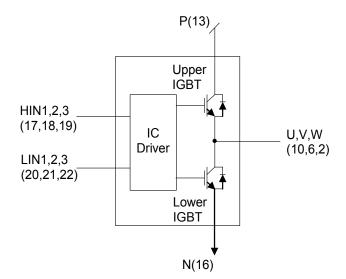

#### **Equivalent Block Diagram**

# STK531U369A-E

# **Module Pin-Out Description**

| Pin | Name   | Description                                         |

|-----|--------|-----------------------------------------------------|

| 1   | VB3    | High Side Floating Supply Voltage 3                 |

| 2   | W, VS3 | Output 3 - High Side Floating Supply Offset Voltage |

| 3   | -      | Without Pin                                         |

| 4   | -      | Without Pin                                         |

| 5   | VB2    | High Side Floating Supply voltage 2                 |

| 6   | V,VS2  | Output 2 - High Side Floating Supply Offset Voltage |

| 7   | -      | Without Pin                                         |

| 8   | -      | Without Pin                                         |

| 9   | VB1    | High Side Floating Supply voltage 1                 |

| 10  | U,VS1  | Output 1 - High Side Floating Supply Offset Voltage |

| 11  | -      | Without Pin                                         |

| 12  | -      | Without Pin                                         |

| 13  | Р      | Positive Bus Input Voltage                          |

| 14  | -      | Without Pin                                         |

| 15  | -      | Without Pin                                         |

| 16  | N      | Negative Bus Input Voltage                          |

| 17  | HIN1   | Logic Input High Side Gate Driver - Phase U         |

| 18  | HIN2   | Logic Input High Side Gate Driver - Phase V         |

| 19  | HIN3   | Logic Input High Side Gate Driver - Phase W         |

| 20  | LIN1   | Logic Input Low Side Gate Driver - Phase U          |

| 21  | LIN2   | Logic Input Low Side Gate Driver - Phase V          |

| 22  | LIN3   | Logic Input Low Side Gate Driver - Phase W          |

| 23  | FAULT  | Fault output                                        |

| 24  | ISO    | Current monitor output                              |

| 25  | VDD    | +15V Main Supply                                    |

| 26  | VSS    | Negative Main Supply                                |

| 27  | ISD    | Over current detection and setting                  |

| 28  | RCIN   | Fault clear time setting output                     |

| 29  | тн     | Thermistor output                                   |

#### **Test Circuit**

(The tested phase : U+ shows the upper side of the U phase and U- shows the lower side of the U phase.)

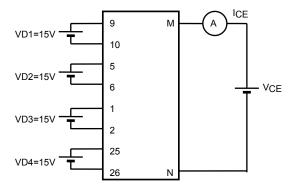

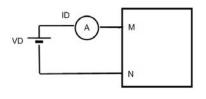

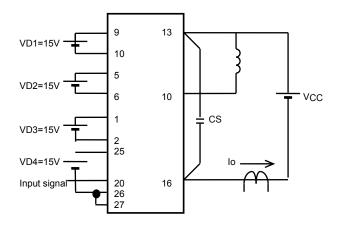

#### ■ ICE / IR(BD)

|   | U+ | V+ | W+ | U- | V- | W- |

|---|----|----|----|----|----|----|

| M | 13 | 13 | 13 | 10 | 6  | 2  |

| N | 10 | 6  | 2  | 16 | 16 | 16 |

|   | U(BD) | V(BD) | W(BD) |

|---|-------|-------|-------|

| M | 9     | 5     | 1     |

| N | 26    | 26    | 26    |

Fig.1

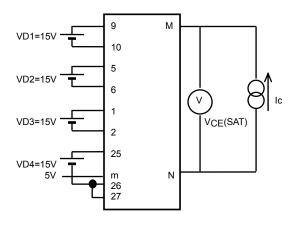

#### ■ VCE(SAT) (Test by pulse)

|   | U+ | V+ | W+ | U- | V- | W- |

|---|----|----|----|----|----|----|

| М | 13 | 13 | 13 | 10 | 6  | 2  |

| N | 10 | 6  | 2  | 16 | 16 | 16 |

| m | 17 | 18 | 19 | 20 | 21 | 22 |

Fig.2

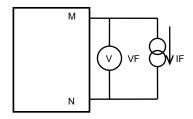

### ■ VF (Test by pulse)

|   | U+ | V+ | W+ | U- | V- | W- |

|---|----|----|----|----|----|----|

| M | 13 | 13 | 13 | 10 | 6  | 2  |

| N | 10 | 6  | 2  | 16 | 16 | 16 |

Fig.3

#### ■ ID

|   | VD1 | VD2 | VD3 | VD4 |

|---|-----|-----|-----|-----|

| M | 9   | 5   | 1   | 25  |

| N | 10  | 6   | 2   | 26  |

Fig.4

#### ■ ISD

Fig.5

■ Switching time (The circuit is a representative example of the lower side U phase.)

Fig.6

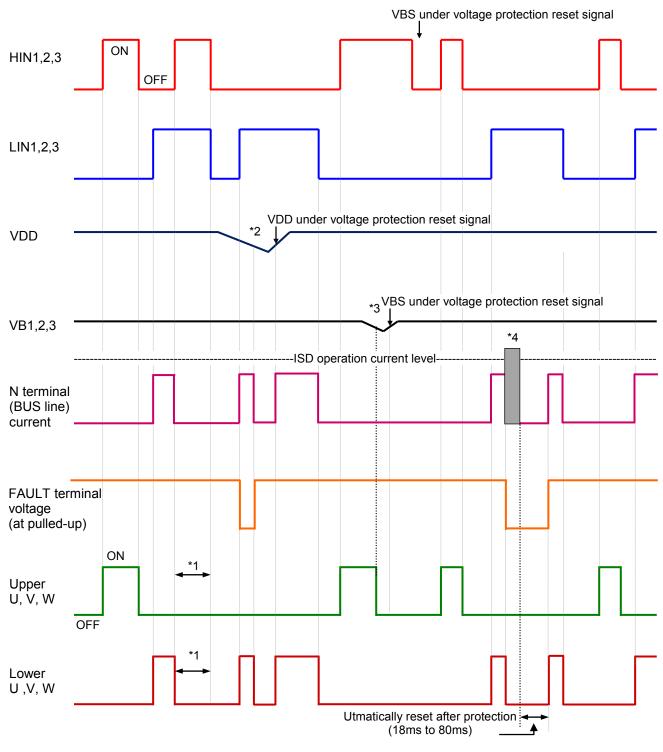

#### **Input / Output Timing Chart**

Fig. 7

#### Notes

- \*1: Diagram shows the prevention of shoot-through via control logic. More dead time to account for switching delay needs to be added externally.

- \*2: When  $V_{DD}$  decreases all gate output signals will go low and cut off all of 6 IGBT outputs. When  $V_{DD}$  rises the operation will resume immediately.

- \*3: When the upper side gate voltage at VB1, VB2 and VB3 drops only, the corresponding upper side output is turned off. The outputs return to normal operation immediately after the upper side gate voltage rises.

- \*4: In case of over current detection, all IGBT's are turned off and the FAULT output is asserted. Normal operation resumes in 18 to 80ms after the over current condition is removed.

# Logic level table

| _   |       |        |               |               |                   |       |

|-----|-------|--------|---------------|---------------|-------------------|-------|

|     | INPUT | OUTPUT |               |               |                   |       |

| HIN | LIN   | ОСР    | Upper<br>IGBT | Lower<br>IGBT | U,V,W             | FAULT |

| Н   | L     | OFF    | ON            | OFF           | Р                 | OFF   |

| L   | Η     | OFF    | OFF           | ON            | N                 | OFF   |

| L   | اـ    | OFF    | OFF           | OFF           | High<br>Impedance | OFF   |

| Н   | Н     | OFF    | OFF           | OFF           | High<br>Impedance | OFF   |

| Х   | X     | ON     | OFF           | OFF           | High<br>Impedance | ON    |

Fig. 8

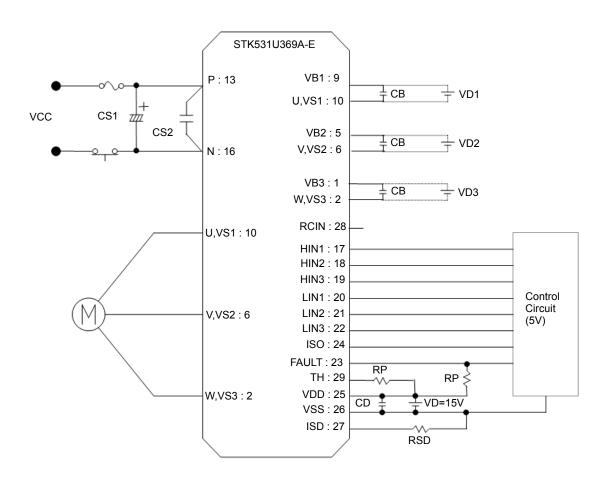

# **Sample Application Circuit**

Fig.9

#### **Recommended Operating Condition**

| Item                        | Symbol          | Conditions                            | MIN  | TYP | MAX  | Unit |

|-----------------------------|-----------------|---------------------------------------|------|-----|------|------|

| Supply voltage              | V <sub>CC</sub> | P to N                                | 0    | 280 | 450  | V    |

| Des divises supply welfages | VD1,2,3         | VB1 to U, VB2 to V, VB3 to W          | 12.5 | 15  | 17.5 | W    |

| Pre-driver supply voltage   | VD4             | V <sub>DD</sub> to V <sub>SS</sub> *1 | 13.5 | 15  | 16.5 | V    |

| PWM frequency               | fPWM            |                                       | 1    | -   | 20   | kHz  |

| Dead time                   | DT              | Turn-off to Turn-on                   | 2    | -   | -    | μs   |

| Allowable input pulse width | PWIN            | ON and OFF                            | 1    | -   | -    | μs   |

| Tightening torque           |                 | 'M3' type screw                       | 0.6  | -   | 0.9  | Nm   |

<sup>\*1 :</sup> Pre-drive power supply (VD4=15±1.5V) must have the capacity of Io=20mA (DC), 0.5A (Peak).

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Usage Precaution**

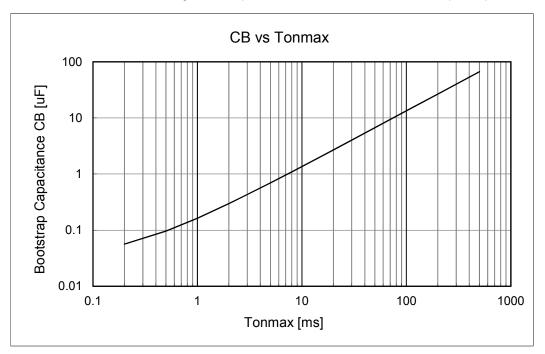

- 1. This IPM includes bootstrap diode and resistors. Therefore, by adding a capacitor "CB", a high side drive voltage is generated; each phase requires an individual bootstrap capacitor. The recommended value of CB is in the range of 1 to 47μF, however this value needs to be verified prior to production. If selecting the capacitance more than 47μF (±20%), connect a resistor (about 20Ω) in series between each 3-phase upper side power supply terminals (VB1, 2, 3) and each bootstrap capacitor. When not using the bootstrap circuit, each upper side pre-drive power supply requires an external independent power supply.

- 2. It is essential that wirning length between terminals in the snubber circuit be kept as short as possible to reduce the effect of surge voltages. Recommended value of "CS" is in the range of 0.1 to 10μF.

- 3. "ISO" (pin24) is terminal for current monitor. High current may flow into that course when short-circuiting the "ISO" terminal and "VSS" terminal. Please do not connect them.

- 4. "FAULT" (pin23) is open DRAIN output terminal (Active Low). Pull up resistor is recommended more than 6.8kΩ.

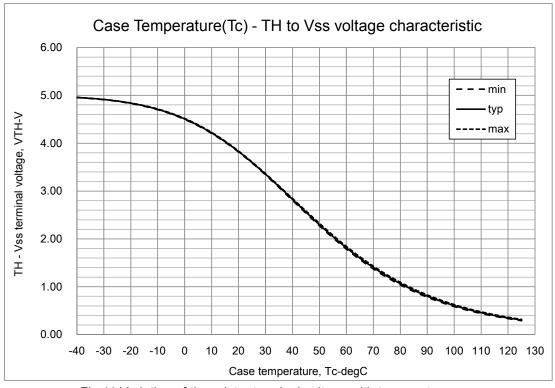

- 5. Inside the IPM, a thermistor used as the temperature monitor for internal subatrate is connected between V<sub>SS</sub> terminal and TH terminal therefore, an external pull up resistor connected between the TH terminal and an external power supply should be used. The temperature monitor example application is as follows, please refer the Fig.10, and Fig.11 below.

- 6. Pull down resistor of  $33k\Omega$  is provided internally at the signal input terminals. An external resistor of 2.2k to  $3.3k\Omega$  should be added to reduce the influence of external wiring noise.

- 7. The over current protection feature is not intended to protect in exceptional fault condition. An external fuse is recommended for safety.

- 8. The level of the over current protection might be changed from IPM design value when "ISD" terminal and "V<sub>SS</sub>" terminal are shorted at external. Be confirm with actual application("N" terminal and "V<sub>SS</sub>" terminal are shorted at internal).

- 9. The level of the over current protection is adjustable with the external resistor "RSD" between "ISD" terminal and "VSS" terminal.

- 10. When input pulse width is less than 1.0µs, an output may not react to the pulse. (Both ON signal and OFF signal)

This data shows the example of the application circuit, does not guarantee a design as the mass production set.

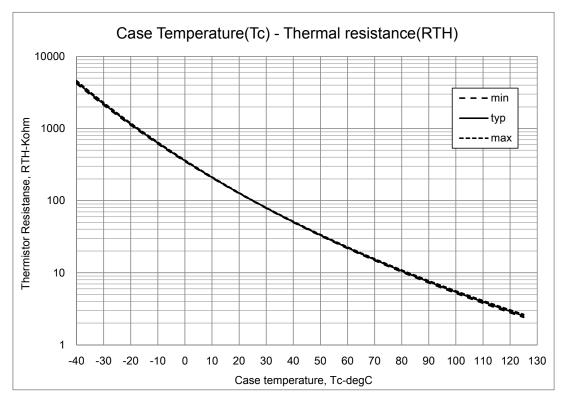

#### The characteristic of thermistor

| Parameter                | Symbol           | Condition  | MIN  | TYP  | MAX  | Unit |

|--------------------------|------------------|------------|------|------|------|------|

| Posistanos               | R <sub>25</sub>  | Tc = 25°C  | 99   | 100  | 101  | kΩ   |

| Resistance               | R <sub>100</sub> | Tc = 100°C | 5.18 | 5.38 | 5.60 | kΩ   |

| B-Constant (25 to 50 °C) | В                |            | 4208 | 4250 | 4293 | K    |

| Temperature Range        |                  |            | -40  | -    | +125 | °C   |

Fig.10 Variation of thermistor resistance with temperature

Fig.11 Variation of thermistor terminal voltage with temperature (39k $\Omega$  pull-up resistor, 5V)

#### CB capacitor value calculation for bootstrap circuit

#### **Calculate conditions**

| Parameter                                                | Symbol | Value | Unit |

|----------------------------------------------------------|--------|-------|------|

| Upper side power supply.                                 | VBS    | 15    | V    |

| Total gate charge of output power IGBT at 15V.           | QG     | 89    | nC   |

| Upper limit power supply low voltage protection.         | UVLO   | 12    | V    |

| Upper side power dissipation.                            | IDmax  | 400   | μA   |

| ON time required for CB voltage to fall from 15V to UVLO | TONmax | -     | S    |

#### Capacitance calculation formula

Thus, the following formula are true  $VBS \times CB - QG - IDMAX \times TONMAX = UVLO \times CB$  therefore,  $CB = (QG + IDMAX \times TONMAX) \ / \ (VBS - UVLO)$

The relationship between TONMAX and CB becomes as follows. CB is recommended to be approximately 3 times the value calculated above. The recommended value of CB is in the range of 1 to  $47\mu\text{F}$ , however, this value needs to be verified prior to production.

Fig. 12 Tonmax - CB characteristic

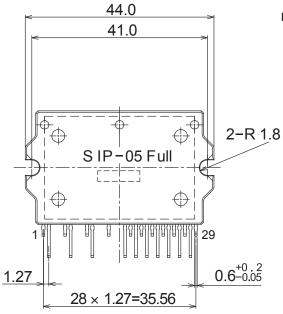

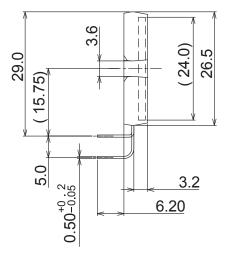

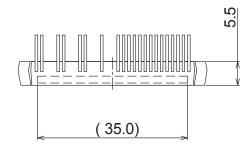

# **Package Dimensions**

unit: mm

The tolerances of length are  $\pm -0.5$ mm unless otherwise specified.

#### SIP29 44x26.5

CASE 127CH ISSUE O

missing pin: 3, 4, 7, 8, 11, 12, 14, 15

#### STK531U369A-E

#### ORDERING INFORMATION

| Device        | Package                    | Shipping (Qty / Packing) |

|---------------|----------------------------|--------------------------|

| STK531U369A-E | SIP29 44x26.5<br>(Pb-Free) | 11 / Tube                |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re